# Designing and Analyzing Decoders for Optimal Efficiency in Digital Systems, Leads to a Comparative Review

Mai Abu Baqar Computer System Engineering Department, Faculty of Engineering, Al-Balqa Applied University, Al Salt, Jordan Ibtehal M. Mishal Computer System Engineering Department, Faculty of Engineering, Al-Balqa Applied University, Al Salt, Jordan Razan H. Hiasat Computer System Engineering Department, Faculty of Engineering, Al-Balqa Applied University, Al Salt, Jordan

## ABSTRACT

Decoders are crucial in digital systems since they convert input signals into specified output configurations. This study seeks to conduct a comprehensive assessment of decoder design and analysis to get maximal efficiency in digital systems. The study entails an extensive examination of many decoding techniques, assessing their effectiveness in diverse digital system applications. This study aims to offer valuable insights into the optimal methods for developing decoders to improve performance in digital systems via the comparison of various decoding techniques.

#### **Keywords**

Decoder; digital system; efficiency; design analysis; comparative review

## 1. INTRODUCTION

Modern technologies depend heavily on digital systems, which are fundamental elements across several sectors. Enhancing the design and analysis of decoders is essential for improving the overall performance of digital systems. This study emphasizes the crucial function of decoders in digital systems, detailing their role in transforming encoded data into a human-readable format, with applications in memory systems, data compression, and communication protocols.[1].

The efficient transformation of encoded data into readable formats is a fundamental characteristic of digital systems, with decoders significantly contributing to this objective. This study analyzes several decoding approaches, their design factors, and conducts a comparative assessment to identify the most effective solutions for digital system applications.[2]

The paper elaborates that obtaining maximum efficiency in digital system decoders necessitates a thorough review of the underlying circuitry, including fundamental logic gates, Boolean operations, and the overarching architectural design utilized in the decoder. It highlights the benefits of developing larger decoders using a structured approach that includes smaller decoder components, hence improving overall efficiency via parallel processing and targeted optimization of the smaller parts [3][4].

Using a design approach that incorporates smaller decoder components to construct larger decoders has been shown to improve overall efficiency. This technique entails breaking down the decoding process into smaller, more manageable sub-tasks that may be addressed by separate decoders. This method promotes parallel processing, minimizes decoding duration, and allows for targeted optimization of the smaller decoder units. The ability to create a 3x8 decoder using several 2x4 decoders illustrates the efficacy of this modular design approach [5].

This comparative research will investigate the intricacies of decoder design and analysis, concentrating on methodologies that seek to reduce power consumption, lower latency, and enhance overall efficiency. The findings of this study will benefit academics, engineers, and practitioners engaged in digital system design and optimization.

Decoders can efficiently perform complicated logical processes by mapping input signals to appropriate output configurations using truth tables [6]. This method offers a versatile and efficient framework for managing logic processing within the digital system, hence enhancing the system's overall efficiency and functionality.

To improve the efficiency of digital systems, it is crucial to investigate the many technologies utilized in decoder design and analysis. A notable technology for constructing decoders is the programmed method. Programmable decoders employ reconfigurable logic components, such field-programmable gate arrays or sophisticated programmable logic devices, enabling the modification of decoding circuitry. This adaptability facilitates the implementation of various decoding algorithms and functionality, addressing the needs of different digital systems. The alterable characteristics of these decoders facilitate effective resource use and faster design iterations, making them ideal for applications requiring regular updates or modifications.

Another method for decoder design is the application-specific integrated circuit approach. ASIC decoders are custom integrated circuits tailored for a particular decoding function or application. Utilizing the inherent advantages of ASIC technology, including superior performance, minimal power consumption, and compact size, ASIC decoders may attain remarkable efficiency and customized functionality for specific digital system applications. The trade-off, however, is the higher initial design and manufacturing expenses, which may restrict their application in fast changing or budget-conscious sectors.

Another technique for decoder design is the Microcontroller-Based Decoders approach. Microcontroller-based decoders utilize the programmable features of microcontrollers to execute adaptable and changeable decoding tasks. Through microcontroller programming, designers may customize the decoding logic to fulfill the distinct requirements of various digital system applications. This method is a cost-effective and quick prototyping process. Digital system designers may develop adaptable, reconfigurable, and economical decoder implementations that adapt to the evolving requirements of their applications, hence improving the overall efficiency and adaptability of the digital system.

The paper shows that the choice between different technologies depends on the specific requirements of the digital system, such as performance, power, flexibility, and cost. Programmable decoders offer adaptability and rapid design iterations, while ASIC decoders excel in terms of performance and power efficiency. By understanding the strengths and limitations of these technologies, digital system designers can make informed decisions to optimize the efficiency and effectiveness of their decoder implementations, ultimately enhancing the overall performance of the digital system.

#### 2. LITERATURE REVIEW

#### 2.1 Understanding Decoder Internal Circuit

The decoder's internal circuit is a fundamental component of digital systems, tasked with converting input signals into a specific output configuration. A decoder typically contains numerous input lines and generates various output lines based on the input combination. A decoder's internal circuit is specifically intended to facilitate the selection of a particular output line by analyzing the binary input pattern.

The fundamental structure of a decoder consists of logic gates, including AND, OR, and NOT gates, within its internal circuit. The gates are interconnected in a precise arrangement to process the input signals and produce the corresponding output. The quantity of input and output lines in a decoder is established by the precise demands of the application.

A decoder's internal circuit decodes the input and chooses the appropriate output line according to the given binary pattern. The process is done by logic gates that utilize Boolean logic operations to determine the output based on the input combination.

Optimal performance in digital systems relies heavily on the efficient design and analysis of the internal circuitry of a decoder. Through a comprehensive comprehension of the complexities of the internal circuitry and the strategic optimization of its design, it becomes feasible to limit the amount of power consumed, decrease the amount of time it takes for data to be processed, and improve the overall effectiveness and productivity of digital system applications.

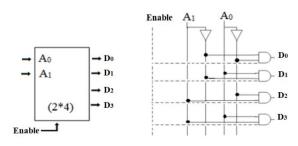

Figure one shows a 2\*4 decoder block diagram and the internal design of the 2\*4 decoder.

Figure 1: The block diagram and internal circuit of 2\*4 decoder

Where table 1 illustrate the truth table of the 2\*4 decoder.

Table 1: The truth table of 2\*4 decoder.

| A1 | A0 | OUTPUT |

|----|----|--------|

| 0  | 0  | D0     |

| 0  | 1  | D1     |

| 1  | 0  | D2     |

| 1  | 1  | D3     |

### 2.2 Constructing Larger Decoders through Modular Integration of Smaller Decoders

Another option approach to enhancing efficiency in digital systems involves the building of a larger decoder utilizing several smaller decoders [7], with an understanding of the decoder's underlying circuitry. This method involves breaking down the decoding process into smaller, manageable tasks that may be executed by separate decoders. This strategy may boost the overall efficiency and performance of the decoding process.

Utilizing a sequence of smaller decoders to create a larger decoder enables parallel decoding, significantly decreasing the overall decoding time[8]. This approach is especially beneficial in scenarios requiring the concurrent decoding of many input signals.

The use of many smaller decoders to create a larger decoder is an effective approach to enhance the efficiency and performance of digital systems. This method can markedly improve the system's overall efficacy by employing concurrent decoding and optimizing smaller decoders for specific tasks.

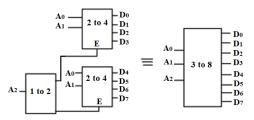

The following figure demonstrates how to construct a  $3 \times 8$  decoder using a set of  $2 \times 4$  decoders.

## Figure 2: Building a 3\*8 decoder using a group of 2\*4 decoders.

In order to guarantee that the group of  $2\times4$  decoders depicted in figure 2 functions as a  $3\times8$  decoder, please consult the decision maker truth table provided in Table 2. All combinations in this table are accurately implemented in this design and there is no distinction between the two designs.

| Table 2: The truth table of a 3*8 decoder. |

|--------------------------------------------|

|--------------------------------------------|

| 2. The truth table of a 5 o decoder. |    |    |        |  |  |

|--------------------------------------|----|----|--------|--|--|

| A2                                   | A1 | A0 | OUTPUT |  |  |

| 0                                    | 0  | 0  | D0     |  |  |

| 0                                    | 0  | 1  | D1     |  |  |

| 0                                    | 1  | 0  | D2     |  |  |

| 0                                    | 1  | 1  | D3     |  |  |

| 1                                    | 0  | 0  | D4     |  |  |

| 1                                    | 0  | 1  | D5     |  |  |

| 1                                    | 1  | 0  | D6     |  |  |

| 1                                    | 1  | 1  | D7     |  |  |

|                                      |    |    |        |  |  |

2.3 Using decoders to implement logic functions: Decoders may perform logical operations in digital systems. By carefully designing the decoder's connections and inputs, it is possible to create a circuit that performs accurate logic operations. This approach facilitates a more adaptable and efficient use of decoders in digital systems.

A frequently used method entails employing a decoder to implement a truth table for a certain logic function. By correlating the decoder's inputs with each of the possible input combinations of the logic function, the decoder may effectively compute the output of the logic function for each input combination. This method is quite beneficial for simplifying complex logical processes and reducing the overall complexity of the digital system.

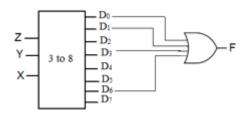

Assume the function F (X,Y,Z) =  $\sum m (0, 1, 3, 6)$ , then the figure 3 shows how to design the full circuit using 3×8 decoder.

Figure 3: Implementing a function using a decoder.

In summary, utilizing decoders to implement logic functions in digital systems offers a versatile and efficient means of handling complex logic operations. By leveraging the capabilities of decoders in conjunction with other logic gates, designers can optimize the performance and functionality of digital systems while minimizing complexity[9].

#### 2.4 Review of decoder design approaches

Various techniques are employed in the domain of digital system design and optimization to develop decoders. Every method possesses unique advantages and disadvantages that must be carefully assessed to determine the optimal strategy for a certain application.

#### 2.4.1 Programmable Logic Devices

Programmable Logic Devices, such as Field-Programmable Gate Arrays and Complex Programmable Logic Devices, are commonly employed for the development of decoders.[10] Programmable Logic Devices (PLDs) provide design freedom and may be reprogrammed to perform various decoding functions, making them ideal for a diverse variety of applications. Nevertheless, they could exhibit increased energy consumption and restricted speed in comparison to specialized hardware implementations

The adaptability of PLDs is attributed to their reprogrammability, allowing designers to modify the decoder functionality to satisfy the particular needs of a digital system[11]. This adaptability is especially beneficial during the design and development process, as the decoder specifications may vary or alter. Utilizing PLDs enables designers to swiftly alter the decoder logic without incurring expensive redesigns or the production of new hardware. Furthermore, the parallel processing capabilities of PLDs, exemplified by FPGAs, may be utilized to construct highperformance decoder circuits. The intrinsic parallelism of PLDs facilitates simultaneous processing of many input signals, resulting in expedited decoding [12] times and enhanced overall system performance.

Despite the benefits of PLDs, they may demonstrate somewhat elevated power consumption and diminished speed[13] relative to Application-Specific Integrated Circuits designed for certain decoding functions. Still, the design versatility and quick prototyping features of PLDs frequently overcome these small limitations, becoming them a favored option for constructing decoders in digital systems.

#### 2.4.2 Application-Specific Integrated Circuits

Application-Specific Integrated circuits are optimized for specific decoding tasks, providing exceptional performance and minimal power consumption. Nevertheless, they necessitate substantial upfront design expenses and lack the flexibility of reprogrammable electronic devices.

Application-Specific Integrated circuits are customized circuitry built for certain decoding functions[14]. These tailored circuits are engineered for superior performance and reduced power consumption, rendering them ideal for applications with strict efficiency demands.

The primary benefit of ASICs is their capacity to deliver highperformance decoding functionalities specifically designed for the precise requirements of the digital system. By constructing the decoder circuitry from the foundation, ASICs may eradicate superfluous logic and optimize the decoding process, leading to enhanced performance and reduced power consumption relative to more general-purpose alternatives.

This specific design methodology entails considerable trade-offs. The initial design and development expenses for ASICs are generally significantly more than those for more adaptable technologies such as Programmable Logic devices. Furthermore, once an ASIC-based decoder is manufactured, its functionality is not easily adaptable, constraining the system's flexibility[15].

Despite these constraints, ASICs continue to be a preferred option for high-volume, high-performance decoding applications where efficiency is essential and the elevated design costs are acceptable. Utilizing the fundamental advantages of specialized hardware, ASIC-based decoders provide outstanding performance and power efficiency, rendering them a crucial resource for designers aiming to optimize digital systems.

#### 2.4.3 Microcontroller-Based Decoders

Microcontrollers, when combined with software-based decoding algorithms, offer an economical and adaptable method for implementing decoders. While they provide the advantage of being adaptable to software upgrades, they may have restrictions when it comes to speed and real-time processing capabilities.

Microcontroller-Driven Decoders provide a cost-effective and flexible method for their implementation[16]. These systems utilize the programmability of microcontrollers, enabling the execution of software-based decoding algorithms. This method has the benefit of smooth upgrades via software updates, allowing designers to modify the decoding capabilities to meet evolving demands.

Nevertheless microcontroller-based decoders may encounter constraints regarding speed and real-time processing capabilities. The effectiveness of these systems is mainly based upon the microcontroller's processing capability and clock speed[17], which may impose limitations for applications requiring highspeed or low-latency decoding. The software-based nature of the decoding technique may generate overhead that affects overall system performance.

Although these possible constraints, microcontroller-based decoders can serve as an affordable and adaptable option for various digital system applications. The capacity to enhance decoding capabilities via software updates is very beneficial, enabling designers to modify and refine the system over time. By carefully evaluating performance needs and trade-offs, microcontroller-based decoders might serve as a feasible choice for designers aiming for a balance among cost, flexibility, and overall system efficiency.

#### 2.4.4 Comparative Analysis

When evaluating these technologies, it is important to take a hierarchical approach that analyzes the distinct features and capabilities of each in a structured manner.

Initially, evaluate the cost considerations. Programmable logic devices often encounter higher initial costs [18]; however, they provide design flexibility and programmability, making them ideal for advancement and experimentation. Application-Specific Integrated Circuits, conversely, show reduced per-unit costs in high-volume production, although they need significant initial design expenditures[19]. Microcontroller-based systems offer a more cost effective, although may be deficient in the performance capabilities necessary for specific applications [20].

Following that, evaluate the power consumption and speed performance of each technique. Programmable Logic Devices may demonstrate more energy consumption[21] than specialized hardware implementations like as Application-Specific Integrated Circuits, which are designed for certain decoding functions[22]. Microcontroller-based decoders might show limitations for speed and real-time processing capabilities[23].

Ultimately, evaluate the adaptability and scalability of the various technologies, Programmable Logic Devices succeed in this capacity, as they can be reprogrammed to execute many decoding functions, making them suitable for a variety of applications[24]. Application-Specific Integrated Circuits, while their great performance, lack the flexibility of reprogrammable devices[25][26]. Microcontroller-based solutions have the benefit of software upgradability; yet, they may encounter difficulties in scaling to meet the requirements of complex digital systems[27].

By utilizing a hierarchical analysis of these technologies that evaluates cost, performance, and flexibility, designers and engineers can make informed decisions regarding the most appropriate decoding technique for their particular digital system needs, resulting in improved efficiency and overall system performance. Programmable Logic Devices (PLDs) are well suited for prototyping and experimentation because they can be reprogrammed. On the other hand, Application-Specific Integrated Circuits (ASICs) are chosen for high-volume manufacturing when there are strict performance requirements. Microcontroller-based solutions provide a cost-effective and adaptable option, but they may not be suited for applications that need high-speed or real-time performance.

Ultimately, the choice of a decoding technique should be determined by the precise needs of the digital system, taking into account considerations such as efficiency, cost, and flexibility to adapt and expand.

#### 3. CONCLUSION

In the end, the effective configuration and examination of the internal circuitry of decoders are essential for maximizing the efficiency of digital systems. Efficiency and performance may be greatly improved by employing techniques such as building a bigger decoder using a group of smaller decoders and utilizing decoders to execute logic tasks. Furthermore, conducting a comparative examination of decoding technologies, such as Programmable Logic Devices, Application-Specific Integrated Circuits, and Microcontroller-Based Decoders, emphasizes the significance of thoroughly evaluating the pros and cons of each approach to identify the most suitable technique for a specific application.

For engineers and designers working on digital systems, it is crucial to comprehend the unique characteristics of each technology and make well-informed decisions throughout decoder development in order to maximize the efficiency and performance of digital systems. By utilizing the insights obtained from this research, developers of digital systems may make informed decisions that are in line with the particular needs and demands of their projects, resulting in enhanced efficiency and performance in the digital systems they create.

#### **4. REFERENCES**

- [1] J. Hagenauer, M. Moerz and A. J. Schaefer, "Analog decoders and receivers for high speed applications".

- [2] Y. Afriyie and M. I., "Multiple Bits Error Detection and Correction in RRNS Architecture using the MRC and HD Techniques".

- [3] B. Koo, J. Kim, J. H. Lee, N. Eum, J. Kim and H. Cho, "Channel decoder architecture of OFDM based DMB system".

- [4] M. Tikekar, C. Huang, C. Juvekar, V. Sze and A. P. Chandrakasan, "Decoder Hardware Architecture for HEVC".

- [5] A. M. A. Hussien, M. S. Khairy, A. Khajeh, A. M. Eltawil and F. Kurdahi, "A Class of Low Power Error Compensation Iterative Decoders".

- [6] J. Zhou, J. Wu, D. Huang, X. Fang and X. Zhu, "Design of decoders based on memristors".

- [7] K. Gummidipudi, N. Engin and S. Sawitzki, "Scalable Reconfigurable Channel Decoder Architecture for Future Wireless Handsets".

- [8] B. Han, R. Wang, Z. Wang, S. Dong, W. Wang and W. Gao, "HEVC decoder acceleration on multi-core X86 platform".

- [9] M. H. B. Jamaa, K. Mohanram and G. D. Micheli, "Novel library of logic gates with ambipolar CNTFETs: opportunities for multi-level logic synthesis".

- [10] B. J. LaMeres, "Programmable Logic".

- [11] D. Rossi et al., "Application Space Exploration of a Heterogeneous Run-Time Configurable Digital Signal Processor".

- [12] J. Lee, B. Lee, J. Thorpe, K. Andrews, S. Dolinar and J. Hamkins, "A scalable architecture of a structured LDPC decoder".

- [13] J. Wang, C. Chang and C. Yeh, "Analysis and design of high-speed and low-power CMOS PLAs".

- [14] P. Urard, L. Paumier, V. Heinrich, N. Raina and N. Chawla, "A 360mW 105Mb/s DVB-S2 Compliant Codec based on 64800b LDPC and BCH Codes enabling Satellite-Transmission Portable Devices".

- [15] B. Plunkett and D. C. Yen, "Computational efficiency: adaptive computing vs. ASICs".

- [16] R. Petrella and M. Tursini, "An Embedded System for Position and Speed Measurement Adopting Incremental Encoders".

- [17] B. Choi, K. Choi, S. Ko and A. Morales, "Efficient real-time implementation of MPEG-4 audiovisual decoder using DSP and RISC chips".

- [18] C. Fey and D. Paraskevopoulos, "A techno-economic assessment of application-specific integrated circuits: Current status and future trends".

- [19] C. Fey and D. Paraskevopoulos, "Studies in LSI technology economics. II. A comparison of product costs using MSI, gate arrays, standard cells, and full custom VLSI".

- [20] P. S. Shenoy, V. T. Buyukdegirmenci, A. M. Bazzi and P. T. Krein, "System level trade-offs of microprocessor supply voltage reduction".

- [21] J. Lamoureux and W. Luk, "An Overview of Low-Power Techniques for Field-Programmable Gate Arrays".

- [22] N. Beucher, N. Bélanger, Y. Savaria and G. Bois, "A Methodology to Evaluate the Energy Efficiency of Application Specific Processors".

- [23] C. Herglotz, D. Springer, M. Reichenbach, B. Stabernack and A. Kaup, "Modeling the Energy Consumption of the HEVC Decoding Process".

- [24] R. Dubey, P. Agarwal and M. Vasantha, "Programmable Logic Devices for Motion Control—A Review".

- [25] R. Selow, H. S. Lopes and C. R. E. Lima, "A comparison of FPGA and FPAA technologies for a signal processing application".

- [26] C. Paiz and M. Porrmann, "The Utilization of Reconfigurable Hardware to Implement Digital Controllers: a Review".

- [27] A. E. Vasil'ev, T. Ivanova, D. Cabezas and Q. Luong, "Microcontroller-based embedded system equipment development for research and educational support".